# Controllable Electrical Properties of Metal-Doped In<sub>2</sub>O<sub>3</sub> Nanowires for High-Performance Enhancement-Mode Transistors

Xuming Zou,<sup>†</sup> Xingqiang Liu,<sup>†</sup> Chunlan Wang,<sup>†</sup> Ying Jiang,<sup>‡</sup> Yong Wang,<sup>‡</sup> Xiangheng Xiao,<sup>†</sup> Johnny C. Ho,<sup>§,\*</sup> Jinchai Li,<sup>†</sup> Changzhong Jiang,<sup>†</sup> Qihua Xiong,<sup>⊥</sup> and Lei Liao<sup>†,\*</sup>

<sup>†</sup>Department of Physics and Key Laboratory of Artificial Micro- and Nano-structures of Ministry of Education, Wuhan University, Wuhan 430072, China, <sup>‡</sup>Department of Materials Sciences & Engineering, Zhejiang University, Hangzhou 310058, China, <sup>§</sup>Department of Physics and Materials Science, City University of Hong Kong, Tat Chee Avenue, Kowloon, Hong Kong SAR, China, and <sup>⊥</sup>Department of Physics, Nanyang Technological University, Singapore 639798

**ABSTRACT** In recent years,  $ln_2O_3$  nanowires (NWs) have been widely explored in many technological areas due to their excellent electrical and optical properties; however, most of these devices are based on  $ln_2O_3$  NW field-effect transistors (FETs) operating in the depletion mode, which induces relatively higher power consumption and fancier circuit integration design. Here, n-type enhancement-mode  $ln_2O_3$  NW FETs are successfully fabricated by doping different metal elements (Mg, Al, and Ga) in the NW channels. Importantly, the resulting threshold voltage can be effectively modulated through varying the metal (Mg, Ga, and Al) content in the NWs. A series of scaling effects in the mobility, transconductance, threshold voltage, and source—drain current with respect to the device channel length are also observed. Specifically, a small gate delay time (0.01 ns) and high on-

current density (0.9 mA/ $\mu$ m) are obtained at 300 nm channel length. Furthermore, Mg-doped In<sub>2</sub>O<sub>3</sub> NWs are then employed to fabricate NW parallel array FETs with a high saturation current (0.5 mA), on/off ratio (>10<sup>9</sup>), and field-effect mobility (110 cm<sup>2</sup>/V·s), while the subthreshold slope and threshold voltage do not show any significant changes. All of these results indicate the great potency for metal-doped In<sub>2</sub>O<sub>3</sub> NWs used in the low-power, high-performance thin-film transistors.

KEYWORDS: In<sub>2</sub>O<sub>3</sub> nanowires · field-effect transistors · enhancement-mode · controllable threshold voltage · doping

n the past few years, due to exceptional physical properties, semiconductor nanowires (NWs) have been widely studied and explored as fundamental building blocks for various technological applications.<sup>1–5</sup> Among many NW materials, metal oxide NWs such as  $In_2O_3$  is a promising candidate for active device materials in next-generation electronics,<sup>6–8</sup> memory devices,<sup>9,10</sup> displays,<sup>11,12</sup> and chemical and biosensors<sup>13–16</sup> because of their chemical stability, wide band gap ( $\sim$ 3.6 eV), optical transparency, and high field-effect carrier mobility ( $\mu_{FF}$ ). However, most of these In<sub>2</sub>O<sub>3</sub> NW field-effect transistors (FETs) operate in the n-type accumulation or depletion mode (D-mode) which exhibits nonzero current at zero gate bias and negative threshold voltage ( $V_{\rm th}$ ). These D-mode devices are beneficial for quantitative and scalable sensing applications since

the signals come from the modulation of the channel rather the contacts,<sup>17–19</sup> but in the area of electronic circuits, both D-mode and enhancement mode (E-mode) devices are needed.<sup>20–24</sup> E-mode FETs typically operate with off-current at zero gate bias and positive  $V_{\rm th}$ . They are more preferable to their D-mode counterparts as there is no need to utilize a gate voltage to switch off the E-mode devices such that the power consumption is relatively lower, circuit design is simpler for integration, and the transport of charge carriers can be accurately modulated by the gate structure.<sup>20</sup> Although the E-mode NW FETs reveal more unique advantages, it is still a big challenge to control these device operations (D-mode versus E-mode) with the detailed electrical characterization performed. For example, Lee et al. have architected the surface of ZnO NWs to modify the fabricated

\* Address correspondence to liaolei@whu.edu.cn, johnnyho@cityu.edu.hk.

Received for review November 14, 2012 and accepted December 10, 2012.

Published online December 10, 2012 10.1021/nn305289w

© 2012 American Chemical Society

VOL.7 • NO.1 • 804-810 • 2013

JAI

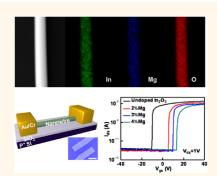

Figure 1. SEM images of (a) undoped  $In_2O_3$ , (b) Mg $-In_2O_3$ , (c) Al-doped  $In_2O_3$ , (d) Ga-doped  $In_2O_3$  NWs grown on a (100) silicon substrate coated with 1 nm thick Au film. The scale bars are 2  $\mu$ m. (e) XRD patterns of the as-synthesized NWs.

transistor characteristics with the smooth NWs for the D-mode device operation and corrugated NWs for the E-mode FETs.<sup>23</sup> Also, Zhou *et al.* have explored the different surface passivation schemes in order to control the electrical properties such as  $V_{\rm th}$  of the  $\ln_2O_3$  NW devices.<sup>25</sup> All of these approaches have heavily relied on the modulation of surface and/or interface states of the metal oxide NW surfaces to alter their corresponding electronic transport properties, in which this NW surface modulation may be difficult for the large-scale integration due to the wire-to-wire variation in their surfaces.

In this paper, instead of controlling the surface properties, we present a simple technique to achieve n-type E-mode In<sub>2</sub>O<sub>3</sub> NW FETs by simply doping different metal elements (Mg, Ga, and Al) during the NW synthesis. The resulting device threshold voltage (V<sub>th</sub>) can be effectively modulated by adjusting the metal (Mg, Ga, and Al) content in the NWs with negligible changes in other electrical properties such as  $\mu_{\rm FE}$ , subthreshold slope (SS), and saturation current  $(I_{on})$ . Furthermore, electron beam lithography (EBL) technique is used to study the device scaling of Mg-doped In<sub>2</sub>O<sub>3</sub> NW FETs, and a series of scaling effects are observed when the channel length is reduced. High-performance E-mode Mg-doped In<sub>2</sub>O<sub>3</sub> NW parallel array devices are also fabricated, which further illustrates the technological potency of metaldoped In<sub>2</sub>O<sub>3</sub> NWs for the next-generation low-power thin-film transistors (TFTs).

### **RESULTS AND DISCUSSION**

The typical scanning electron microscopy (SEM) images of undoped, Mg-, Al-, and Ga-doped  $In_2O_3$  NWs are shown in Figure 1a-d, respectively. It is clear that the NW morphology is not evidently affected by the doping process. All NWs are grown with diameters of 40–70 nm and lengths of tens to hundreds of micrometers. In order to confirm the metal dopant incorporation within the NW crystal structure, X-ray diffraction (XRD) is performed. Figure 1e displays the XRD spectra taken from undoped, Mg-, Al-, and Gadoped  $In_2O_3$  NWs. The strongest (222) peak indicates that all grown  $In_2O_3$  NWs consist of the cubic crystal

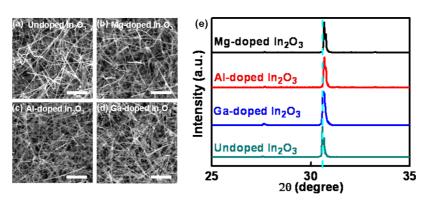

Figure 2. (a) TEM image of a typical Mg-doped  $ln_2O_3$  NW. The scale bar is 100 nm. (b) Corresponding HRTEM image taken from the circled area in (a). The scale bar is 1 nm. (Inset) SAED pattern of the same NW, illustrating a cubic crystal structure with the  $\langle 100 \rangle$  growth direction. (c) Highangle annular dark-field image of the Mg-doped  $ln_2O_3$  NW and the corresponding EDS elemental mapping. The scale bar is 50 nm.

structure in both doped and undoped samples. Although the dopants do not modify the NW crystal structure in this study, they induce the distortion of crystal lattice as evidenced by the shift of (222) peaks. This shift toward the higher angle reveals a narrowing of the lattice constant, which can be attributed to the metal ion (Ga<sup>3+</sup>, Al<sup>3+</sup>, Mg<sup>2+</sup>) substitution in In sites of the lattice since all metal ions here have a smaller ionic radius than the one of  $\ln^{3+}.2^{6}$

To further characterize the metal-doped  $In_2O_3$  NWs, Mg-doped  $In_2O_3$  NWs are studied by the high-resolution transmission electron microscopy (HRTEM) in details. As depicted in Figure 2a, the typical NW appears relatively homogeneous without any significant domain boundaries, indicating the single-crystalline nature. The HRTEM image (Figure 2b) and corresponding selected area electron diffraction (SAED) pattern (top inset, Figure 2b) further illustrate its cubic crystal structure. In addition, indexing the SAED pattern demonstrates the  $\langle 100 \rangle$  direction being the NW growth direction. All

VOL.7 • NO.1 • 804-810 • 2013 A

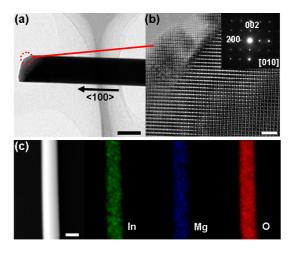

Figure 3. Electrical properties of back-gated Mg-doped  $\ln_2O_3$  NW FETs fabricated on the silicon substrate. (a) Schematic and (inset) SEM image of a representative single NW FET fabricated with Cr/Au (20 nm/40 nm) electrodes and heavily doped silicon substrates covered with 110 nm thick thermally grown SiO<sub>2</sub>. The scale bar is 5  $\mu$ m. (b)  $I_{ds}$  versus  $V_{gs}$  curves at  $V_{ds} = 1$  V for the back-gated FET with different Mg doping concentration (0, 2, 3, and 4 wt %). (c) Family of  $I_{ds} - V_{ds}$  curves for the 2 wt % Mg doping concentration with  $V_{gs} = 25$  to 5 V in -5 V steps from top to bottom. The average (d)  $\mu_{FEr}$  (e)  $V_{thr}$ , and (f) SS values of 15 NW devices versus Mg doping concentration.

of these results are consistent with the former study on undoped  $In_2O_3$  NWs.<sup>27</sup> The energy-dispersive X-ray spectrometry (EDS) is also performed to exhibit the homogeneous distribution of In, Mg, and O atoms along the NW body (Figure 2c), which suggests uniform chemical composition along the NW axial direction.

In addition to the crystal structure, to shed light on the investigation of the electrical properties of In<sub>2</sub>O<sub>3</sub> NWs with different Mg doping concentration, NW FETs (Figure 3) are fabricated with different NW channels grown with various weight ratios of MgO powder in the source materials, which are set to 10:0.5:2, 10:1:2, and 10:2:2 (In<sub>2</sub>O<sub>3</sub>/MgO/graphite). The corresponding Mg content of the grown NWs is then assessed by EDS, and the doping concentration (weight ratio) is estimated to be  $\sim$ 2, 3, and 4 wt %, respectively. The devices are measured at a fixed condition including temperature, humidity, and  $V_{qs}$  sweep rate so as to avoid the disturbance of uncertainty random circumstance factor. The hysteresis of  $I_{ds} - V_{qs}$  is observed when  $V_{qs}$  is swept from -40 V to +40 V and back to -40 V; however, the hysteresis does not show significant difference for these devices (see Supporting Information Figure S1). Figure 3b shows the representative  $I_{ds}$  versus  $V_{qs}$  curves for different Mg doping concentration, and they all exhibit the standard n-type transistor behavior as expected. The threshold voltages, V<sub>th</sub> (confirmed from the horizontal intercept of a linear part in  $I_{ds}^{1/2}$  vs  $V_{qs}$ plot), are -10, 5.6, 10, and 13.6 V for the Mg doping concentration of 0, 2, 3, and 4 wt %, accordingly, producing a remarkable shift to more positive voltages with the increasing Mg concentration. This shift indicates that the D-mode In<sub>2</sub>O<sub>3</sub> NW FETs are successfully transformed into the E-mode when the Mg doping is increased. Figure 3c depicts the output characteristics recorded from the same device (2 wt % Mg), showing

that  $I_{ds}$  increases linearly with  $V_{ds}$  at low  $V_{ds}$  and saturates at high  $V_{ds}$ . The linear regime can be attributed to the good ohmic contacts between the Cr/Au electrodes and the NWs. The pinch-off and  $I_{ds}$  saturation suggest that the carrier transport is completely controlled by the gate bias.

Moreover, a statistical analysis to correlate the changes in  $\mu_{\text{FE}}$ ,  $V_{\text{th}}$  and SS to the Mg doping concentration is also performed. The average and standard deviation for these quantities are calculated based on 15 NW FETs for each type. The  $\mu_{\text{FE}}$  is estimated using the equation

$$\mu_{\rm FE} = \frac{g_{\rm m}L^2}{C_{\rm q}V_{\rm ds}} \tag{1}$$

in the linear operation regime. Here  $g_m = dI_{ds}/dV_{gs}$  is the transconductance, and  $L = 3 \mu m$  is the nanowire device channel length.  $C_g$  is the capacitance of the back gate which can be estimated by utilizing the cylinder on-plane model:

$$C_{\rm g} = \frac{2\pi\varepsilon_0\varepsilon_{\rm r}L}{\ln(4h/d)} \tag{2}$$

where  $\varepsilon_0$  is the permittivity of free space,  $\varepsilon_r$  is the dielectric constant of SiO<sub>2</sub>, h = 110 nm is the thickness of the SiO<sub>2</sub> layer that is measured by ellipsometry, and d (50 ± 15 nm) is the NW diameter. Using the estimated capacitance values and measured device parameters, the average  $\mu_{FE}$  values are estimated to be 188, 190, 177, and 123 cm<sup>2</sup>/V · s for the Mg doping concentration of 0, 2, 3, and 4 wt %, respectively (Figure 3d). Considering the enhanced ionized impurity scattering for the increased Mg doping, this mobility degradation is expected but not significant. Then the average  $V_{th}$  value also changes from -6.4 to 8.9 V as the Mg concentration increases (Figure 3e); this positive shift is believed to be associated with the reduced carrier concentration (n), which can be

VOL.7 • NO.1 • 804-810 • 2013 A

IAI

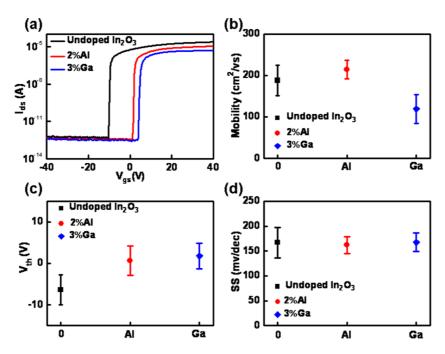

Figure 4. (a)  $I_{ds}$  vs  $V_{gs}$  curves at  $V_{ds}$  = 1 V for the undoped, Al-doped, and Ga-doped In<sub>2</sub>O<sub>3</sub> NW FETs. Average (b)  $\mu_{FFr}$  (c)  $V_{th}$ , and (d) SS values of 15 FETs fabricated with undoped, Al-doped, and Ga-doped In<sub>2</sub>O<sub>3</sub> NWs as the device channels.

estimated by this equation:

$$n = \frac{4C_{\rm g}(V_{\rm gs} - V_{\rm th})}{\pi q d^2 L} \tag{3}$$

Here, *q* is the electronic charge. At  $V_{gs} = 20$  V, the average values of *n* are ~6.4 × 10<sup>18</sup> cm<sup>-3</sup> for undoped ln<sub>2</sub>O<sub>3</sub>, ~4.0 × 10<sup>18</sup> cm<sup>-3</sup> for 2 wt % Mg, ~2.9 × 10<sup>18</sup> cm<sup>-3</sup> for 3 wt % Mg, and ~2.7 × 10<sup>18</sup> cm<sup>-3</sup> for 4 wt % Mg. This degradation of carrier concentration is possibly due to the compensation of the oxygen vacancies by the acceptor Mg.<sup>28–30</sup> Meanwhile, the reduced carrier concentration and  $\mu_{FE}$  also lead to the slight decrease of  $I_{on}$ . In view of the standard deviation, the SS value does not show any significant change (Figure 3f), indicating that the Mg doping has little affection for the interfacial trap density here.<sup>1</sup> Moreover, all of these devices show an extraordinary on/off current ratio (>10<sup>7</sup>), exhibiting excellent semiconducting characteristics for device applications.

At the same time, AI and Ga doping are also performed in the  $In_2O_3$  NW synthesis in order to evaluate their doping effect on the NW device characteristics. This way, the NWs are grown with the same weight ratio of the source material ( $In_2O_3/AI_2O_3$  or  $Ga_2O_3/$ graphite = 10:1:2) for each case. On the basis of the EDS analysis, the AI and Ga doping concentration is estimated to be 2 and 3 wt %, respectively. Figure 4a gives the representative  $I_{ds}$  versus  $V_{gs}$  curves for the undoped, AI-doped, and Ga-doped  $In_2O_3$  NW FETs. Similar to the one of Mg doping, these devices exhibit a standard n-type FET behavior with a positive voltage shift in  $V_{th}$ . The average and standard deviations for  $\mu_{FE'}V_{th'}$  and SS values calculated based on 15 FETs are shown in Figure 4b–d, accordingly. Compared to the Ga doping, the Al-doped  $In_2O_3$  NW FET has slightly better electrical performance in  $\mu_{FE}$  and saturation current, which can be attributed to the difference in the carrier scattering and electron concentration caused by these two different impurity ions. Notably, the SS values depicted in Figure 4d are all very similar with the undoped case, indicating that small amounts of Al<sup>3+</sup> or Ga<sup>3+</sup> have an inferior effect on the interfacial trap density, as well. In the future studies, when the doping concentration is further increased, a more effective control over  $V_{th}$  can also be expected.

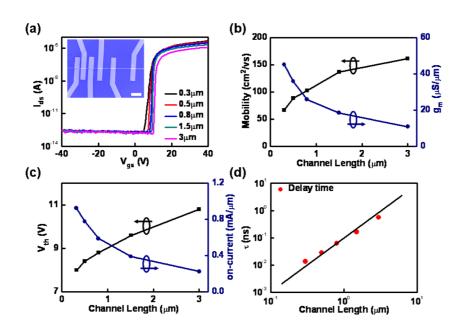

To demonstrate the potency of these metal-doped In<sub>2</sub>O<sub>3</sub> NWs for the scaled transistors, the dependence of device electrical properties on the channel length is studied. The FET used in this study is fabricated by EBL with the Mg-doped In<sub>2</sub>O<sub>3</sub> NW channel (3 wt % Mg; diameter of 53 nm). Figure 5a presents the corresponding  $I_{ds} - V_{gs}$  curves for different channel lengths  $(0.3, 0.5, 0.8, 1.5, and 3 \mu m)$  at a fixed drain bias of 1 V with the inset showing the device SEM image. It can be clearly seen that the device exhibits standard n-type E-mode FET behaviors, even though the channel length is decreased to 0.3  $\mu$ m. Because the off-current  $(\sim 10^{-13} \text{ A})$  is maintained at the similar value and oncurrent increases with the reduced channel length, a large on/off current ratio (>10<sup>8</sup>) is achieved at L =0.3  $\mu$ m. The changes in other typical electrical characteristics ( $\mu_{\text{FE}}, g_{\text{m}}, V_{\text{th}}$ , and on-current) are also illustrated in Figure 5b,c. As the channel length is decreased, the  $V_{\rm th}$  shifts from 10.8 V ( $L = 3 \,\mu$ m) to 8 V ( $L = 0.3 \,\mu$ m), and this negative shift can be well explained by the charge-sharing model. According to this model, when

VOL.7 • NO.1 • 804-810 • 2013

807

Figure 5. (a)  $I_{ds}$  vs  $V_{gs}$  curves for various channel lengths at fixed  $V_{ds} = 1$  V. The inset is the SEM image of the device that was fabricated by EBL with the Mg-doped In<sub>2</sub>O<sub>3</sub> NW channel. The scale bar is 2  $\mu$ m. (b) Plots of  $\mu_{FE}$  and  $g_m$  vs channel length. (c) Plots of  $V_{th}$  and on-current (at  $V_{ds} = 1$  V and  $V_{gs} = 40$  V) vs channel length. (d) Plots of intrinsic delay  $\tau$  vs channel length. The solid linear line is a fit to the data point.

the channel is scaled, the effective channel length would reduce since the charges that are depleted by the source and drain junctions cannot be neglected for shorter channel; as a result, the  $V_{\rm th}$  value that used to create a charge accumulation in the channel would also get decreased.<sup>31</sup> In addition, assuming the effective channel width equals the NW diameter, due to the reduced channel resistance, a larger  $g_{\rm m}$  (45.1  $\mu$ S/ $\mu$ m) and on-current (0.9 mA/ $\mu$ m, under  $V_{ds}$  = 1 V and  $V_{qs}$  = 40 V) can be obtained, as well, at  $L = 0.3 \ \mu m$ . Importantly, this current density is comparable to that of the state-of-the-art Si MOSFETs ( $\sim$ 1 mA/ $\mu$ m). On the other hand, Figure 5b shows that  $\mu_{FE}$  is decreased gradually with reduced channel length. This is probably because the parasitic contact resistance cannot be neglected in shorter channel FETs; otherwise, the short channel length here may become comparable to the mean free path of charge carriers and lead to the quasi-ballistic transport.<sup>31,32</sup> Another important parameter, the intrinsic gate delay time  $(\tau)$  which provides a frequency limitation for the transistor operation,<sup>33</sup> is also discussed here. It is calculated by this equation:

$$\tau = \frac{C_{\rm g}}{g_{\rm m}} = \frac{L^2}{\mu_{\rm eff} V_{\rm ds}} \tag{4}$$

As shown in Figure 5d, the values of  $\tau$  decrease from 0.56 ns ( $L = 3 \mu m$ ) to 0.01 ns ( $L = 0.3 \mu m$ ); the resulting formations of the devices are fit with  $L^2$ . According to the projected cutoff frequency  $(f_T)$  equation

$$f_{\rm T} = \frac{1}{2\pi\tau} \tag{5}$$

the value of  $f_{\rm T}$  can be as large as up to 16 GHz at  $V_{\rm ds}$  = 1 V, indicating that Mg-doped In<sub>2</sub>O<sub>3</sub> NW FETs have great potency for high-speed devices with the low power consumption.

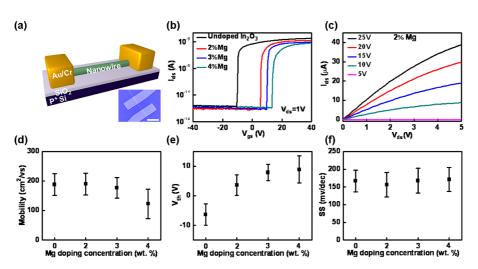

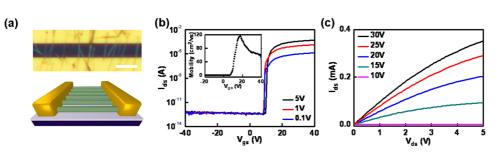

Also, a Mg-doped In<sub>2</sub>O<sub>3</sub> NW (3 wt % Mg) parallel array FET is then fabricated to prove the feasibility of large-scale integration of these NWs for TFT applications. Figure 6a shows the optical image and schematic of the device, while Figure 6b gives the corresponding I<sub>ds</sub>-V<sub>gs</sub> curves, exhibiting a typical n-type E-mode FET behavior as expected. Under  $V_{ds} = 5$  V and  $V_{qs} = 40$  V, it achieves a saturation current of 0.5 mA and a large on/ off current ratio (>10<sup>9</sup>). Furthermore, the  $\mu_{FE}$  value at  $V_{\rm ds} = 1$  V can be estimated with the equation<sup>34</sup>

$$\mu_{\rm FE} = \frac{g_{\rm m}L^2}{NC_{\rm g}V_{\rm ds}} \tag{6}$$

Here, N = 20 is the number of NWs contained in the channel. On the basis of this equation, the peak mobility is estimated to be  $\sim$ 110 cm<sup>2</sup>/V·s (Figure 6b inset). This mobility value is on the same level of that of state-of-the-art semiconductor carbon nanotube networks, which is calculated using the same cylinder-onthe-plane model.<sup>35</sup> Moreover, the SS value is  $\sim$  148 mV/ dec, and  $V_{\rm th}$  is ~8.8 V, which are similar to those of the single NW FET. Notably, as compared to the single NW FET, the average current of each NW reduces slightly. This can be attributed to the increased parasitic capacitance that is caused by the misaligned and broken NWs in the channel.<sup>36</sup>  $I_{ds}$  versus  $V_{ds}$  relation at various  $V_{qs}$  values is also shown in Figure 6c, indicating that the carrier transport in the channel can be completely controlled by the gate bias since  $I_{ds}$  increases linearly with  $V_{ds}$  and saturates at higher  $V_{ds}$ . All of these results suggest that Mg-doped In<sub>2</sub>O<sub>3</sub> NW parallel array FETs can be used for high-performance E-mode TFTs. In the

VOL.7 • NO.1 • 804-810 • 2013

IAI

Figure 6. Electrical characteristics of the Mg-doped  $\ln_2O_3$  NW (3 wt % Mg) parallel array FET. (a) (Top) optical and (bottom) schematic of a back-gated Mg-doped NW array FET. The scale bar is 5  $\mu$ m. (b)  $I_{ds}-V_{gs}$  curves at  $V_{ds} = 0.1$ , 1, and 5 V, respectively, and about 20 NWs bridging source/drain. (Inset) Mobility assessment of this NW array device under  $V_{ds} = 1$  V. (c)  $I_{ds}-V_{ds}$  curves with  $V_{qs} = 30$  to 10 V in -5 V steps from top to bottom.

future, further improvement of the device performance could be expected by optimizing the NW density, reducing channel length, and using a top-gated structure with high-k dielectrics.

## CONCLUSIONS

In summary, n-type enhancement-mode  $In_2O_3$  NW FETs are successfully fabricated by doping different metal elements (Mg, Ga, and Al) in the NW channels, which show adjustable threshold voltage with different doping

concentration without affecting device characteristics much. Meanwhile, when the channel length is reduced, a series of scaling effects are observed for the Mg-doped  $\ln_2O_3$  NW FETs such as the shorter delay time down to 0.01 ns. Furthermore, Mg-doped  $\ln_2O_3$  NWs are also employed to fabricate n-type E-mode NW parallel array FETs, and impressive saturation current (0.5 mA), on/off ratio (>10<sup>9</sup>) and mobility (110 cm<sup>2</sup>/V·s) are obtained, indicating the great potency of Mg-doped  $\ln_2O_3$  NWs for low-power, high-performance TFTs.

#### **METHODS**

**Nanowire Synthesis.** The metal-doped  $\ln_2O_3$  NWs used in this study were synthesized in a horizontal tube furnace utilizing a simple chemical vapor deposition (CVD) method. A mixture of doping metallic oxide powder,  $\ln_2O_3$  powder, and graphite powder with the weight ratio of 10:1:2 was placed into a quartz boat, and silicon substrates coated with 1 nm of gold catalyst were then placed in the downstream position about 10 cm away from the evaporation source. Then, the whole setup was inserted into a quartz tube reactor. The source and substrate were heated to 1100 and 900 °C, respectively, and kept at this temperature for 1 h under a constant flow of gas (argon/oxygen = 100:1) at a flow rate of 200 sccm. When the system had cooled to room temperature, a large amount of NWs was formed on the surface of the silicon substrate.

**FET Fabrication and Characterization.** After growth, the NWs were transferred to the precleaned highly doped p-type silicon substrates with a thermally grown 110 nm thick SiO<sub>2</sub> layer. Then the substrates were spin-coated with MMA and PMMA, and the EBL (JEOL 6510 with NPGS) was employed to define the source and drain pattern. The Cr/Au (20 nm/40 nm) electrodes were completed by metal evaporation and lift-off processes. Electrical performance of fabricated back-gated NW FETs was performed with the Lake Shore TTPX Probe Station and Agilent 4155C semiconductor parameter analyzer.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. We acknowledge the 973 grant of MOST (No. 2011CB932700), MOE NCET-10-0643, and NSFC grant (Nos. 11104207, 61222402, 91123009, and 10975109), Hubei Province Natural Science Foundation (2011CDB271), the Natural Science of Jiangsu Grant (BK2011348), The Grant of State Key Laboratory of Advanced Technology for Materials Synthesis and Processing (Wuhan University of Technology), and the General Research Fund of the Research Grants Council of Hong Kong SAR, China, under Project Nos. CityU 101210 and CityU 101111.

Supporting Information Available: Hysteresis characteristics of the Mg-doped  $In_2O_3$  NW FET. This material is available free of charge via the Internet at http://pubs.acs.org.

#### **REFERENCES AND NOTES**

- 1. Duan, X. F.; Niu, C. M.; Sahi, V.; Chen, J.; Parce, J. W.; Empedocles, S.; Goldman, J. L. High-Performance Thin-Film Transistors Using Semiconductor Nanowires and Nanoribbons. *Nature* **2003**, *425*, 274–278.

- Li, Y.; Qian, F.; Xiang, J.; Lieber, C. M. Nanowire Electronic and Optoelectronic Devices. *Mater. Today* **2006**, *9*, 18–27.

Lieber, C. M. Nanoscale Science and Technology: Building a

- Big Future from Small Things. *MRS Bull.* 2003, 28, 486–491.

Huang, Y.; Duan, X. F.; Cui, Y.; Lauhon, L. J.; Kim, K. H.; Lieber,

- Huang, Y. Duan, X. P. Cui, Y. Launon, L. J., Kim, K. H. Lieber, C. M. Logic Gates and Computation from Assembled Nanowire Building Blocks. *Science* 2001, *294*, 1313–1317.

- Thelander, C.; Agarwal, P.; Brongersma, S.; Eymery, J.; Feiner, L. F.; Forchel, A.; Scheffler, M.; Riess, W.; Ohlsson, B. J.; Goesele, U.; Samuelson, L. Nanowire-Based One-Dimensional Electronics. *Mater. Today* **2006**, *9*, 28–35.

- Li, C.; Zhang, D. H.; Han, S.; Liu, X. L.; Tang, T.; Zhou, C. W. Diameter-Controlled Growth of Single-Crystalline In<sub>2</sub>O<sub>3</sub> Nanowires and Their Electronic Properties. *Adv. Mater.* 2003, *15*, 143–146.

- Lee, C.; Srisungsitthisunti, P.; Park, S.; Kim, S.; Xu, X.; Roy, K.; Janes, D. B.; Zhou, C.; Ju, S.; Qi, M. Control of Current Saturation and Threshold Voltage Shift in Indium Oxide Nanowire Transistors with Femtosecond Laser Annealing. *ACS Nano* **2011**, *5*, 1095–1101.

- Nguyen, P.; Ng, H. T.; Yamada, T.; Smith, M. K.; Li, J.; Han, J.; Meyyappan, M. Direct Integration of Metal Oxide Nanowire in Vertical Field-Effect Transistor. *Nano Lett.* 2004, 4, 651–657.

- Li, C.; Ly, J.; Lei, B.; Fan, W.; Zhang, D. H.; Han, J.; Meyyappan, M.; Thompson, M.; Zhou, C. W. Data Storage Studies on Nanowire Transistors with Self-Assembled Porphyrin Molecules. J. Phys. Chem. B 2004, 108, 9646–9649.

- Li, C.; Fan, W.; Straus, D. A.; Lei, B.; Asano, S.; Zhang, D. H.; Han, J.; Meyyappan, M.; Zhou, C. W. Charge Storage Behavior of Nanowire Transistors Functionalized with Bis-(terpyridine)-Fe(II) Molecules: Dependence on Molecular Structure. J. Am. Chem. Soc. 2004, 126, 7750–7751.

- Ju, S.; Facchetti, A.; Xuan, Y.; Liu, J.; Ishikawa, F.; Ye, P.; Zhou, C.; Marks, T. J.; Janes, D. B. Fabrication of Fully Transparent

Nanowire Transistors for Transparent and Flexible Electronics. *Nat. Nanotechnol.* **2007**, *2*, 378–384.

- Ju, S.; Li, J.; Liu, J.; Chen, P.-C.; Ha, Y.-G.; Ishikawa, F.; Chang, H.; Zhou, C.; Facchetti, A.; Janes, D. B.; Marks, T. J. Transparent Active Matrix Organic Light-Emitting Diode Displays Driven by Nanowire Transistor Circuitry. *Nano Lett.* 2008, *8*, 997–1004.

- Curreli, M.; Li, C.; Sun, Y. H.; Lei, B.; Gundersen, M. A.; Thompson, M. E.; Zhou, C. W. Selective Functionalization of In<sub>2</sub>O<sub>3</sub> Nanowire Mat Devices for Biosensing Applications. J. Am. Chem. Soc. **2005**, 127, 6922–6923.

- Li, C.; Zhang, D. H.; Liu, X. L.; Han, S.; Tang, T.; Han, J.; Zhou, C. W. In<sub>2</sub>O<sub>3</sub> Nanowires as Chemical Sensors. *Appl. Phys. Lett.* 2003, *82*, 1613–1615.

- Zhang, D. H.; Liu, Z. Q.; Li, C.; Tang, T.; Liu, X. L.; Han, S.; Lei, B.; Zhou, C. W. Detection of NO<sub>2</sub> down to ppb Levels Using Individual and Multiple In<sub>2</sub>O<sub>3</sub> Nanowire Devices. *Nano Lett.* **2004**, *4*, 1919–1924.

- Li, C.; Curreli, M.; Lin, H.; Lei, B.; Ishikawa, F. N.; Datar, R.; Cote, R. J.; Thompson, M. E.; Zhou, C. W. Complementary Detection of Prostate-Specific Antigen Using In<sub>2</sub>O<sub>3</sub> Nanowires and Carbon Nanotubes. *J. Am. Chem. Soc.* **2005**, *127*, 12484–12485.

- Fan, Z. Y.; Lu, J. G. Gate-Refreshable Nanowire Chemical Sensors. Appl. Phys. Lett. 2005, 86, 123510.

- Cheng, Y.; Xiong, P.; Fields, L.; Zheng, J. P.; Yang, R. S.; Wang, Z. L. Intrinsic Characteristics of Semiconducting Oxide Nanobelt Field-Effect Transistors. *Appl. Phys. Lett.* 2006, *89*, 093114.

- Fan, Z. Y.; Wang, D. W.; Chang, P. C.; Tseng, W. Y.; Lu, J. G. ZnO Nanowire Field-Effect Transistor and Oxygen Sensing Property. *Appl. Phys. Lett.* **2004**, *85*, 5923–5925.

- Fortunato, E. M. C.; Barquinha, P. M. C.; Pimentel, A.; Goncalves, A. M. F.; Marques, A. J. S.; Martins, R. F. P.; Pereira, L. M. N. Wide-Bandgap High-Mobility ZnO Thin-Film Transistors Produced at Room Temperature. *Appl. Phys. Lett.* **2004**, *85*, 2541–2543.

- Ma, R. M.; Dai, L.; Qin, G. G. Enhancement-Mode Metal-Semiconductor Field-Effect Transistors Based on Single n-CdS Nanowires. *Appl. Phys. Lett.* 2007, *90*, 093109.

- 22. Mikkelson, J. A.; Tomasetta, L. R. High-Density GaAs Integrated Circuit Manufacturing. *IEEE Trans. Semicond. Manuf.* **2003**, *16*, 384–389.

- Hong, W.-K.; Sohn, J. I.; Hwang, D.-K.; Kwon, S.-S.; Jo, G.; Song, S.; Kim, S.-M.; Ko, H.-J.; Park, S.-J.; Welland, M. E.; Lee, T. Tunable Electronic Transport Characteristics of Surface-Architecture-Controlled ZnO Nanowire Field Effect Transistors. *Nano Lett.* **2008**, *8*, 950–956.

- Hong, W.-K.; Hwang, D.-K.; Park, I.-K.; Jo, G.; Song, S.; Park, S.-J.; Lee, T.; Kim, B.-J.; Stach, E. A. Realization of Highly Reproducible ZnO Nanowire Field Effect Transistors with n-Channel Depletion and Enhancement Modes. *Appl. Phys. Lett.* **2007**, *90*, 243103.

- Kim, S.; Carpenter, P. D.; Jean, R. K.; Chen, H.; Zhou, C.; Ju, S.; Janes, D. B. Role of Self-Assembled Monolayer Passivation in Electrical Transport Properties and Flicker Noise of Nanowire Transistors. ACS Nano 2012, 6, 7352–7361.

- Chun, H. J.; Choi, Y. S.; Bae, S. Y.; Choi, H. C.; Park, J. Single-Crystalline Gallium-Doped Indium Oxide Nanowires. *Appl. Phys. Lett.* **2004**, *85*, 461–463.

- 27. Hao, Y. F.; Meng, G. W.; Ye, C. H.; Zhang, L. D. Controlled Synthesis of  $In_2O_3$  Octahedrons and Nanowires. *Cryst. Growth Des.* **2005**, *5*, 1617–1621.

- Bierwagen, O.; Speck, J. S. Mg Acceptor Doping of In<sub>2</sub>O<sub>3</sub> and Overcompensation by Oxygen Vacancies. *Appl. Phys. Lett.* 2012, *101*, 102107.

- Ni, J.; Wang, L.; Yang, Y.; Yan, H.; Jin, S.; Marks, T. J.; Ireland, J. R.; Kannewurf, C. R. Charge Transport and Optical Properties of MOCVD-Derived Highly Transparent and Conductive Mg- and Sn-Doped In<sub>2</sub>O<sub>3</sub> Thin Films. *Inorg. Chem.* 2005, 44, 6071–6076.

- Kanai, Y. Electronic Conduction in Mg Doped In<sub>2</sub>O<sub>3</sub> Single Crystals. Jpn. J. Appl. Phys. **1985**, 24, L361–L363.

- 31. Jo, G.; Maeng, J.; Kim, T.-W.; Hong, W.-K.; Jo, M.; Hwang, H.; Lee, T. Effects of Channel-Length Scaling on  $In_2O_3$

Nanowire Field Effect Transistors Studied by Conducting Atomic Force Microscopy. *Appl. Phys. Lett.* **2007**, *90*, 173106.

- Han, S.-J.; Chen, Z.; Bol, A. A.; Sun, Y. Channel-Length-Dependent Transport Behaviors of Graphene Field-Effect Transistors. *IEEE Electron Device Lett.* 2011, *32*, 812–814.

- Xiang, J.; Lu, W.; Hu, Y. J.; Wu, Y.; Yan, H.; Lieber, C. M. Ge/Si Nanowire Heterostructures as High-Performance Field-Effect Transistors. *Nature* 2006, 441, 489–493.

- Fan, Z.; Ho, J. C.; Takahashi, T.; Yerushalmi, R.; Takei, K.; Ford, A. C.; Chueh, Y.-L.; Javey, A. Toward the Development of Printable Nanowire Electronics and Sensors. *Adv. Mater.* 2009, *21*, 3730–3743.

- Wang, C.; Chien, J.-C.; Takei, K.; Takahashi, T.; Nah, J.; Niknejad, A. M.; Javey, A. Extremely Bendable, High-Performance Integrated Circuits Using Semiconducting Carbon Nanotube Networks for Digital, Analog, and Radio-Frequency Applications. *Nano Lett.* **2012**, *12*, 1527–1533.

- Hou, J. J.; Han, N.; Wang, F.; Xiu, F.; Yip, S.; Hui, A. T.; Hung, T.; Ho, J. C. Synthesis and Characterizations of Ternary InGaAs Nanowires by a Two-Step Growth Method for High-Performance Electronic Devices. ACS Nano 2012, 6, 3624– 3630.